posted by

rerofumi

2016/4/2 土曜日 17:54:25

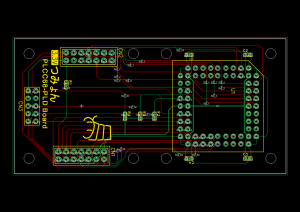

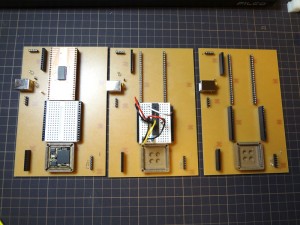

ヒューマンデータが販売している PLCC68 ソケットサイズの PLD シリーズに JTAG コネクタとつみょん形状のソケットを追加するプロトタイピング基板です。

つみょん基板として FPGA や CPLD の実験ができるようになります。

ただ、つみょんソケット規格としては I/Opin が 21本程度しか出せませんので半分以上の I/O は NC でいささか勿体ない作りとなっています。

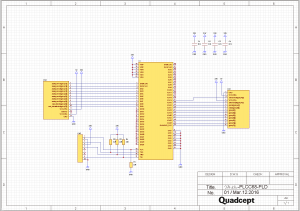

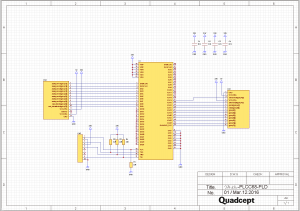

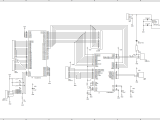

回路図

BOM

| Item |

Size |

Num |

Value |

| R1-4 |

R1608 |

4 |

2.2kΩ |

| C1-4 |

C1608 |

4 |

0.1uF |

| CN1-2 |

CN-2×7 |

2 |

CN-2×7 |

| CN3 |

CN-2×5 |

1 |

JTAGコネクタ |

| U1 |

PLCC68 |

1 |

PLCC68ソケット |

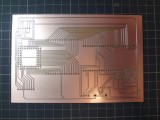

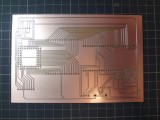

基板

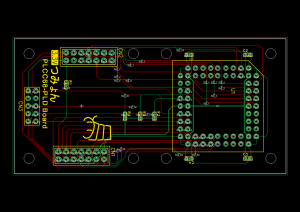

プリント基板のガーバーファイルです。

Download: PLD-PLCC68-Prod1.zip

基板が欲しい方はこのガーバーファイルを FusionPCB なり Elecrow なりに製造依頼することでオンデマンド製造することができます。

スイッチサイエンスPCB で製造したときに使ったガーバーデータそのものになります。

単なる変換基板扱いなので単体動作はしません。

せめてクロックオシレータでも乗っていればと思うのですが、つみょん的にはオシレータを提供する基板を作成して積み重ねるのが正解でしょう。

posted by

rerofumi

2011/12/31 土曜日 0:07:23

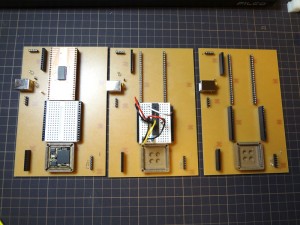

前回に引き続き、ヒューマンデータの PLCC68 PLD シリーズと PSoC3 を載せた汎用プロトタイプボードの作成。主に俺用。

これで大体完成。

使えるピンは多くないけど、中央のブレッドボードでちょこっとテストしたりすることができるお気軽ボード。

ちょこちょこと修正したり、改良したりして 3代目。

使っていると「あ、こここうした方が良いかも」というところがあったり、微妙な問題があったりで作り直しを繰り返していた。

とくに PLCCソケットの向きを痛快に間違えていたというのは痛かった。

主な修正箇所は以下

- 若干立て幅が足りなくてブレッドボードが収まらなかった

- 電源ラインにパイロットLEDを追加

- ブレッドボード脇のIOソケットに +3.3V と GND を引き出し

- PSoC3 に RTC 用の 32.768kHz 水晶を追加

Read the rest of this entry »

posted by

rerofumi

2011/11/28 月曜日 0:01:11

ヒューマンデータの PLCC68 PLD シリーズというのがある。PLD(FPGA/CPLD) を小型モジュール化して PLCC 68 ピンサイズにしたものだ。

DIP(2.54mm) の PLCC ソケットが使えるのでユニバーサル基板とかで工作しやすいというもの。今のところピンも合わせてあるので PLCC シリーズを載せ替えて使う事もできるっぽい。

面白いなーと思って一個買ってあった。IO は少ないけれども、扱いやすいしちょこっと遊んだり実験したりするには十分じゃないかと思ったので。

しかし、これは単なるモジュールなので何かするには基板を起こす必要がある。当たり前と言えば当たり前のお話。

ユニバーサル基板でもなんでも乗せない事には JTAG ケーブルも繋がらない。

なので、これまた実験としていじり倒したい PSoC3 とセットのテストボードをこさえてみようというのが今回のお題。

PSoC3 は以前作成した変換基板ベースで、これまた DIP サイズにしてあるもの。

写真のは CY8C3246 だけれども CY8C3866 も買ってあるので載せ替えられるように。

回路図。

全ピンを引き出しているわけじゃないけれども、そこは無理しても面倒なだけだからそこそこの数引いてあれば良しとするお気楽設計。

CNCで作成、片面ジャンパ3本。

実装や設計のチェックはこれから。本日は基板を作ったところまでに。

まあ、この段階でちょっと設計手直ししたいところが既にあるので、後日また作り直す予定ですが。

posted by

rerofumi

2009/10/3 土曜日 0:43:16

先日部屋を掃除していたら、混沌の奥底から探していた本が発掘された。

「HDLによる高性能ディジタル回路設計」 私がHDLを学習する際に大いに参考となった一冊である。

著者は森岡澄夫。いまやSOMESATで有名な「超電磁P」の森岡氏である。

この本が氏の著書だと言うことに気がついたのはうかつにも森岡氏と会ってから大分たってからのことだったのだけれども、書籍のタイトルを見ただけで「あー、あの本かー」と思ったほどに印象深くかつ参考になる一冊だった。

サブタイトルに「ソフトウェア感覚を離れてハードウェアを意識する」とあるように、ハードウェアとソフトウェアの違いや、ハードウェアはこういう風に設計するんだよといった方針をわかりやすく教えてくれる。

他に類のない良著なのだけれども、これ一冊ですべてが完結するわけではなかったりする。あくまでも「どういった方針で作るのか」で終わっているので、実際に FPGA を設計したりするためには VHDL や VerilogHDL の文法解説書が別に必要になるのだよな。

FPGAに興味があるという初心者は、まずこの本を最初にざっくりと読んでデジタル回路とはどういうものかをつかんでから入るのがオススメ。

CQPICことPIC16F85コンパチCPUのVHDLソースコードも付いてくるよ。

posted by

rerofumi

2009/6/28 日曜日 2:08:52

パラレルポート接続のJTAGタウンロードケーブルと決別してWindows7 RC 64bit を使い始めて数週間。結局 Xilinx と Lattice についてはUSB接続ダウンロードケーブルを買ってしまったので、VMwareのXPから特に問題なく利用も開発もできている状態。しかしALTERAデバイスのダウンロードケーブルだけがない。

ALTERA用についてはTERASIC BLASTERが安いし、それ以前にALTERAは使わないから良いかなーと思って後回し。

一応Cyclone2のブレッドボードとか手元にあったりもするので使えるに超したことはない気がする。

そんなとき「USB-Blasterもどきの制作記事」なるものを知る。おー、なんか使用頻度も高くないからこれで良いんじゃねって気がしてきた。

部品箱をあさったら無事全部そろえることができたのでさくっと作ってみようか。

PIC18F2550 は秋月電子のモジュールを使用する。別件でテストしていたものを使い回し。USB接続のシリアルコンバータ+ちょっとしたマイコンが欲しいときに一番使いやすいモジュールなんじゃなかろうか。

水晶や電源周りにUSBコネクタと一通りケアされているので便利。つか、今回の目的だとこれに抵抗とコネクタ付けるだけ。

適当に作成。間にバッファでも挟むとより使えるものになりそうだけれども、今回はEasyに作りたかったので省略。

マイコンにファームを書き込んで完成。

おお、本当に USB-Blaster として認識されてコンフィグレーションもできた。もちろん、AS Programing もOK。

いやいや、これはお手軽で良いですなあ。

そいや、xilprg派生でUSB-BlasterをImpactからIP利用するプロキシなんてのがあるんだっけ?それを使えばXilinxもコンフィグレーションできるかもね。

posted by

rerofumi

2009/6/6 土曜日 17:00:15

さて、せっかくマルツボードとFPGAを手に入れたのでなんか作るか。ということで、以前CPLDで修行したときの「カップラーメンタイマー」を移植することにした。(CPLD版の制作記 2, 3)

お試しで作るのにちょうど良い題材。

CPLDのときはゲート数も少なく、なんとか詰め込むような感じだったけれども、今回の Lattice FPGA XP2-5E は単純比較で 30倍くらいの規模があるため余裕ありあり。なので、以前はできなかった「時間がきたらアラームが鳴る仕組み」も追加することにする。

アラームのために圧電スピーカを追加している(左上)。

ボタンはSW2~5 の 4つで左から、5分、4分、3分、1分のスタートとなっている。

完成したラーメンタイマーの ispLEVER7.2 プロジェクト。(余計なファイルも混ざっていたらごめん)

Download: ramen_timer_lattice.zip

VHDLのソースコードのみアーカイブ

Download: ramen_timer_lattice_vhdl.zip

動作しているところの動画など。

Read the rest of this entry »

posted by

rerofumi

2009/5/18 月曜日 23:28:43

先日買ったマルツのFPGA学習ベースボードについているパラレルプログラマでうはうはのFPGA生活が送れているかというとさにあらず。この五日間コンフィギュレーションができなくて悪戦苦闘していた。

■ 第一の難関、増設パラレルポートの罠

Lattice の ispVM を起動してダウンロードケーブルを設定することから始まるのだけれども、自動認識に失敗しケーブルを発見することができない。

でまあ、パラレルポート設定の所に 0x0378 とか書いてあるのを見て気がつく。これは、マザーボードというかチップセット内蔵のパラレルポート時のI/Oアドレスだ。うちのは増設カードによるパラレルポートなのでI/Oアドレスが違うはず。

で、見てみたら 0xb400 だったのでこれを手動設定。

これでダウンロードケーブルが認識されて使える様になった。

■ 第二の難関、バウンダリスキャンできない

ところが次の段階であるバウンダリスキャンによるデバイス検出ができずエラーのみが帰ってくる状態に。さっぱりわからないので、超簡易プローブテスタを作成して、マルツボード上を信号が流れているか確認する。

大活躍の超簡易プローブテスタ。

みっちりと調査し、結構な時間をかけてわかったことは、JTAGの信号はちゃんとFPGAに届いていること。たぶん、TDOが受け取れずに 1 オンリーを検出している状態であること。

おまけに、調査しているときなんかの切っ掛けですぐ信号が出てこなくなる現象に遭遇。これに出会うとアプリを起動し直しなのだけれども、4回に1回とかの頻度で起こるのでちときつい。

ちなみに Xilinx モードにしたら Impact で普通にバウンダリスキャンできた(デバイスは不明な奴と表示される)。なのでマルツボードのせいでも、FPGA基板のせいでもなさそうである。

パラレルポートドライバと増設パラレルポートの関係な気がしてきて、やる気はがっつり減退。なにかに頼りたくなってくる。

頼りになる女神降臨(ひだりのほうね)。USBなかわいいアイツ。

まあ、Windows7 のときに「パラレルポート撤廃しようかなー」とかいっていた時はまだ迷いがありながらも検討していたと言うことで。

しかし……。

■ 第三の難関、USBケーブルでもバウンダリスキャンできない

流石にUSBケーブルでもコンフィグできなかった時は目の前まっくらになりましたよ。

今回のLattice基板(&雑誌)3つ買ってあったのだけれども、3つとも駄目ってどういうことよ。いったい何がどうなっているのよさ。

具体的にはパラレルポートの時とは違って、スキャンはできる。できるんだけれども、NO-JTAG という「不明なデバイス」扱いになってしまうという現象。

~~ 2日間の格闘を挟んで ~~

5日を費やしてようやく思い出した。そういや以前にもコンフィグできない問題ってあったよなと。

あれは2007年の Spaltan3E 基板の時。コンフィグできないという問題で一堂騒然。結局波形を揃える必要があるということで、うまくコンフィグできない人は244でバッファを作ってかますか、コンデンサを調整して波形を調整するということになっていたと思う。

その時につくった 74VHC244 なアダプタ。

これを基板とケーブルの間にかますと……。

ばっちりというかあっさりスキャンできるようになりましたよ。こんちくしょうめ。

もちろん、コンフィグもバッチリ。

これで Lattice FPGA基板で開発して遊ぶことができますよ。(目の端にキラリと光ものが)

たぶん、増設パラレルポートで上手くいかないみたいと言う問題と、バッファを噛ました方が良いという問題はそれぞれ別の事象。

私の場合はこうだったという情報までに。

posted by

rerofumi

2009/5/14 木曜日 1:40:39

マルツ電波の「FPGA学習ベースボード」を買ってみましたー。

やあ、デジタル・デザイン・テクノロジー連動付録の Lattice FPGA を使ってみたくなったもので。Lattice FPGAが使えるダウンロードケーブルは手元にないのでどうしたものかなあと考えていたのです。

なひたふさんが XilinxやAlteraのパラレルダウンロードケーブルで Lattice FPGA をプログラミングするサポートダウンローダを公開されているし、Lattice のパラレルダウンロードケーブルの回路図もあるので自作しても良かったりはする。でも、「難しくは無い」けど「面倒くさい」ときってあるよね。その面倒くさいも時には楽しい要素なのだけれども、今回は回避した次第。

それに、テストボードも作るの面倒で、これくらいのがスタートアップにあるのも結構便利なものだったりするのです。いずれは、自作のテストボードができてそれで済ます様になるかもね。

手に取るまで気がつかなかった、というか見落としていたのだけれども。

パラレルポートコネクタがオス型じゃん。

これまで使っていたストロベリーリナックスのパラレルダウンロードケーブル(現在は販売終了)がメス型コネクタだったのでケーブルが合わないよ。中継ぎコネクタでも買ってくるか……。

まあ、ByteBlaster もオス型コネクタだったし、メス型というほうが逆なのかもしれない。

このベースボード、7セグにスイッチにラダー抵抗DACとシリアルって結構バランスの良い学習ボードだと思う。取り敢えずの学習でこの辺は使いやすいしね。汎用I/Oポート端子に245バッファがついているところも初心者向けやマイコン応用用途としてポイント高し。

7セグがダイナミックでなく直繋ぎなのでポートを食い過ぎなのが難点。SRAMがついているとかなり汎用度が高まるんだけれども、まあそのへんはブロックRAMでなんとかするところか。

回路として簡単なのでおまけ的に USBコネクタがついているのだけれども、使える人がどれくらいいるかはちと疑問ではある。

この後に続く、Splatan3E と Cyclone 互換基板の販売が楽しみ。

この手の基板が後々入手できることの安心感は大きいと思うのです。

posted by

rerofumi

2008/10/14 火曜日 21:49:14

去る 2008年10月12日、ニコニコ技術部東海勉強会が名古屋で開かれた。

今回も楽しい発表がたくさん。その中でも電子工作的な視点でオススメなどを。

akira_you氏の15分でサーボを動かすライブハンダ付け実演ショーもなんか間違っている面白さがあったけれども、今回技術的に良かったなーと思ったのが撮影できますPの「秋月300円液晶向けFPGA基板における 電源設計について(PDF)」という発表。

先日できあがった「NEGIBATAKE」というボードでの電源設計と、その実際についてのリポートといった感じ。

このへん原理とかはわかっているけれども、実際にプロダクトとして使うにはという具体例で提示してもらえるとわかりやすい。

まあ、趣味工作でそこまでやる場面がこれまでそんなになかったというのもあるかもしれないけれども。

久しぶりにPLDやりたいなとふつふつ思い始めていたり。

posted by

rerofumi

2007/7/10 火曜日 1:00:11

コンフィギュレーションROMを入手するのがめんどくさいので弄ることはないでしょ、とか思っていたDWMのSpartan3E基板。なんとなく Digikey を覗いてみたら、対象のコンフィギュレーションROM(XCF02S)が 550円程度だったので買ってみる事に。

最も、日本からの Digikey 利用は手数料 2〜3000円がかかるので割安感のためには 4個以上買わないとならないのですが。

てなわけで到着。

梱包はこんな感じ。

ブツ。

ハンダ付けの際はルーペが活躍。

まあ、これくらいなら手はんだでもなんとか。

面倒な場合はブリッジ上等な感じのはんだ多めで取り敢えず盛っておいて、はんだ吸い取り線でブリッジを除去しつつ整えていく感じで作業するのがよろしいかと。

無事バウンダリチェーンに現れた。

最初 J1 をカットするのを忘れていて悩んだのは秘密。試しにLEDピカピカテストをコンフィギュレーションROMに書き込んでみた。

これでダウンロード無しに、電源投入そくピカピカなのです。将来的にはこれでなんか作ってみるかねえ。