posted by

rerofumi

2016/4/2 土曜日 17:54:25

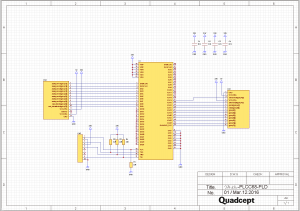

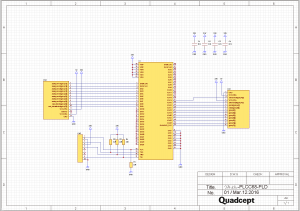

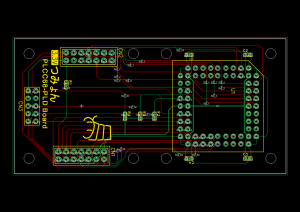

ヒューマンデータが販売している PLCC68 ソケットサイズの PLD シリーズに JTAG コネクタとつみょん形状のソケットを追加するプロトタイピング基板です。

つみょん基板として FPGA や CPLD の実験ができるようになります。

ただ、つみょんソケット規格としては I/Opin が 21本程度しか出せませんので半分以上の I/O は NC でいささか勿体ない作りとなっています。

回路図

BOM

| Item |

Size |

Num |

Value |

| R1-4 |

R1608 |

4 |

2.2kΩ |

| C1-4 |

C1608 |

4 |

0.1uF |

| CN1-2 |

CN-2×7 |

2 |

CN-2×7 |

| CN3 |

CN-2×5 |

1 |

JTAGコネクタ |

| U1 |

PLCC68 |

1 |

PLCC68ソケット |

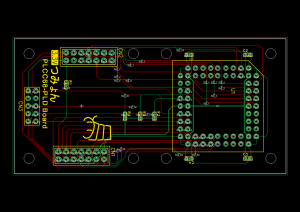

基板

プリント基板のガーバーファイルです。

Download: PLD-PLCC68-Prod1.zip

基板が欲しい方はこのガーバーファイルを FusionPCB なり Elecrow なりに製造依頼することでオンデマンド製造することができます。

スイッチサイエンスPCB で製造したときに使ったガーバーデータそのものになります。

単なる変換基板扱いなので単体動作はしません。

せめてクロックオシレータでも乗っていればと思うのですが、つみょん的にはオシレータを提供する基板を作成して積み重ねるのが正解でしょう。

posted by

rerofumi

2009/10/3 土曜日 0:43:16

先日部屋を掃除していたら、混沌の奥底から探していた本が発掘された。

「HDLによる高性能ディジタル回路設計」 私がHDLを学習する際に大いに参考となった一冊である。

著者は森岡澄夫。いまやSOMESATで有名な「超電磁P」の森岡氏である。

この本が氏の著書だと言うことに気がついたのはうかつにも森岡氏と会ってから大分たってからのことだったのだけれども、書籍のタイトルを見ただけで「あー、あの本かー」と思ったほどに印象深くかつ参考になる一冊だった。

サブタイトルに「ソフトウェア感覚を離れてハードウェアを意識する」とあるように、ハードウェアとソフトウェアの違いや、ハードウェアはこういう風に設計するんだよといった方針をわかりやすく教えてくれる。

他に類のない良著なのだけれども、これ一冊ですべてが完結するわけではなかったりする。あくまでも「どういった方針で作るのか」で終わっているので、実際に FPGA を設計したりするためには VHDL や VerilogHDL の文法解説書が別に必要になるのだよな。

FPGAに興味があるという初心者は、まずこの本を最初にざっくりと読んでデジタル回路とはどういうものかをつかんでから入るのがオススメ。

CQPICことPIC16F85コンパチCPUのVHDLソースコードも付いてくるよ。

posted by

rerofumi

2009/4/18 土曜日 20:31:34

中古のアーケードゲーム基板でギャラクシアンを入手した。

残念ながらオリジナルではなくてコピー基板。オリジナルだと今や5万円くらいの値段がついているところなのだけれども、コピー品なので1.5万円というそこそこのお値段。それでも高めではあるのだけれども、そこはそれ、もう30年近く昔のものなので十分にビンテージな一品でありある意味完動であるだけでもすげえといったところもあるので。

日本で流通していた一枚基板モノだと、プログラムROMは3つ載っていたらしい。32kbit が2つに、16kbit が1つ。バイトで表現すると10kBほど。

これの 32k のところを 7F, 7J、16k のところを 7L と表記しておく。

ところがこのコピー基板ではプログラムROM部分がドーター基板になっていて 16kbit のROMを5個使う形になっていた。

これら複数のプログラムROMを手元の 256kbit(128kbitでも良いけど) UV-EPROM に焼き込んで、一本にまとめてみようというのが今回のチャレンジ。

Read the rest of this entry »

posted by

rerofumi

2007/8/11 土曜日 1:22:29

てなわけで、V850とCPLD CRTCによるインベーダーゲームの完成です。

タイトルはプロジェクト名だった「コメベーダー」をそのままタイトルにしてしまいました。考えるの面倒だったので。

まずは作成成果物の提示ということで、動作している所を紹介するムービーとスクリーンショットから。

ムービーはニコニコ動画にあるのと同じもの。

作成成果物としてのソースコード。

komevader V850 ソースコード

komevader CPLD VHDL ソースコード

CPLDは以前から変わっていないはず。

V850のソースコードも画面周りはCPLDとSRAMが無いと意味がないので参考程度に。でも、音声出力周りは使い回しが効くんじゃないかと。

posted by

rerofumi

2007/8/8 水曜日 12:52:44

トータルでは長いこと続けてきたインベーダーゲームとそれを動作させるハードウェアの制作ですが、ついに完成。

動作の様子はニコニコ動画にアップしてあるので、見てやってくださいな。

ニコニコ動画はアカウントがなくて見れないよ、という方用の動画や、ソフトウェア部分のソースコードと解説などはまたこのあと少しずつ用意していく予定。

posted by

rerofumi

2007/8/6 月曜日 2:35:17

これまでの色々な要素はこれを作るために必要なものだったから。

といった感じで、V850+CPLD CRTC 基板によるインベーダーゲームを制作中。

スクリーンショットは、一応V850+CPLD CRTC 基板実機で動いているものを撮影しているけれども、まだまだ未完成品。

今はソフトウェア作成のターンなので、なかなかここに進捗とかが書きづらく間が空いてしまう次第。(ソフトウェアは本業なもんでいまいち語る事がないのです)

ちなみに、Interface誌の V850 アプリケーションコンテストに応募する予定はありません。

テレビゲーム製作は既に記事になっていることだし。

posted by

rerofumi

2007/7/6 金曜日 1:54:29

細かい調整も終わり、ひとまず CPLD CRTC も予定通りに仕上がった感じ。

高機能じゃないけれどもね。

cpld_ctrc_070706.zip

cpld_ctrc_070706.zip

表示しながらの画面描画実験。

フラッシュビデオ その1

するするとシャッターの様に描かれていくのは、CRTCとCPUのSRAMバスアービトレーションを行っていないから。

CRTCが画面を描いている時というのは一生懸命SRAMからデータを読んでいる時である。そんなときにCPUから読み書きしようとするとバスが衝突してとんでもないアドレスを表示してしまうことになるし、CPUも思ったところに思ったデータが書けないことになる。

そこで、CRTCがSRAMからデータを読み出している期間はCPUからのアクセスを遮断している。この時、CPUがSRAMにアクセスできるのはCRTCが画面を描いていない時、つまりVBLANK期間だけとなる。

その隙を狙って描画するのだが、このテストコードではその VBLANK期間にだいたい5〜6ラインくらい描いているようだ。

CRTCのENABLEを下げて無効にすると画面は真っ暗になるが、フルタイムでSRAMにアクセスできるので 1枚画をその隙に転送するとか、画面をクリアするとかに使う。

posted by

rerofumi

2007/5/14 月曜日 0:42:24

CPLD 内部をほとんどスルーで構成して、V850 から SRAM が読み書きできるかどうかをテストする。

まあ、いくつか不具合があって修正しながらなんとか動作確認ができたのでめでたしめでたし。

不具合の内訳は、配線ミス 2箇所、CPLD の inout(データバス)部分で in の時はハイインピーダンスに設定するあたりが良くわかっていなかったというのが一つ。

ひとまず動作している様に見える CPLD の VHDL ソースとピン設定。

sram_test_cpld.zip

sram_test_cpld.zip

V850側のSRAMチェックソースコード。

v850_sram_check.zip

v850_sram_check.zip

レジスタ設定しか参考にならないと思うけれども。いちお、メモ代わりに。

実際に外部バスへメモリを接続すると、V850側からは 0x100000 以降が外部RAM領域になる。それ未満のアドレスでは、読み出し時は ROM から、書き込み時は外部RAMへと変則的なアクセスとなる。

PM+ で新しいプロジェクト作成時「外部RAMを使うか」という項目があるけれども、ここで「はい」を選ぶとディレクティブの .data 領域(変数や可変データが置かれる領域)が 0x100000 に設定されてしまう。ああ、そういう意味だったのかと思った次第。

今回 SRAM 領域をコンパイラに使われると不具合があるので、内蔵 RAM を使うような設定となることを確認しておく。

配線のリストをちょっと更新。

必要かどうか悩んだV850のクロックを一応CPLDに与える事にした。そのために一部配線を入れ替え。

記事としては面白みが無いところだけれども、私としては動いて一安心という一区切りなのでした。